STUDIA

SOCIETATIS SCIENTIARUM TORUNENSIS

TORUN—POLONIA

| VOL. V NR 4 | SECTIO F (ASTRONOMIA) | 1974 |

STANISŁAW GORGOLEWSKI

Solar and Sidereal Digital Clock

Zegar cyfrowy na czas słoneczny i gwiazdowy

Komunikat

zgloszony przez czł. S. Gorgolewskiego

na posiedzeniu Wydzialu III w dniu 11 XII 1972 r.

Abstract. An integrated circuit digital clock was built which derives, from a temperature stabilized 100 kHz crystal oscillator, two time scales — solar and sidereal with indication of seconds, minutes and hours. Each time scale is displayed in binary code with 19 bits, by means of 5 columns of incandescent lamps with 1, 2, 4, 8 values as well as with remote dials and binary voltage levels.

The sidereal second is derived from 100 kHz by means of a time varying frequency divider with alternate division ratios of 99727 and 99726 ensuring an accuracy better than 1 s per year.

The entire system is fed from a continuously charged CdNi battery of 100 Ah capacity.

To increase the reliability and the flexibility of the previously available time service, based on the transistorized quartz crystal solar clock, digital frequency dividers have been added to provide both solar and sidereal time scales.

The transistorized solar clock of the TKH–1 type produced in Czechoslovakia was used in our observatory eversince 1961. This clock has a well aged 100 kHz crystal capable of 2×10–9 accuracy over a time span of a few days. To improve the reliability of the time service, which recently deteriorated slowly due to the wear of the mechanical parts of the time display unit, two digital clocks have been designed, built, tested and brought into operation. The new system uses only the 100 kHz signal for generation of both time scales by means of the TTL 74 series digital integrated circuits. A total of 33 integrated circuits, 73 transistors, 11 diodes and 38 incandescent indicator lamps are used in this system. The entire system including the TKH–1 crystal oscillator is fed from the 12 V 100 Ah Cd Ni storage battery which is continuously charged from the 220 V AC power line.

The TKH–1 crystal clock requires a positive-ground supply which in turn demands a floating 5V stabilizer for the integrated circuits. The total average current drain of the digital clocks including display is close to 1.4 A.

The 100 kHz sine wave signal of 5.7 V p.t.p. amplitude from the crystal oscillator is converted to voltage pulses by the separating amplifier working in pulse shaper mode as shown in fig. 1. This circuit has about 20 kΩ input impedance and is not sensitive to noise on the —12 V line, because it is only a saturating and level shifting amplifier and not a trigger.

The solar second is generated by 5 decade counters of the SN7490N type preceded by 4 inverters of the SN7400N integrated circuit used as pulse shaper and gating circuit. The 24 h solar time scale is derived from the solar second from the :10 and :6 divider, :10 and :6 divider, :12 and :2 divider. To obtain the :10, :6 and :12 counters the SN7493N :16 circuit was used, the :2 function was obtained from ha1f of the SN7473N dual JK flip-flop, the other half was used in the sidereal clock.

The block diagramme of the solar clock is shown in fig. 2. The divide by 100000 counter has 100 kHz, 10 kHz, 1 kHz, 100 Hz, 50 Hz, 10 Hz and 1 Hz outputs fed through isolation amplifiers but the 1 Hz-output is first mixed with 1 kHz signal that produces 1 kHz tone bursts every second. S1 normally closed, is opened only when one wants to preset the required time before the clock is started. S2 normally open, when contact 1 is closed the clock runs 1000 times faster and the approximate time can be set on the display, when contact 2 is closed the clock runs 10 times faster and contact 3 runs the clock at normal speed for final time setting. At this stage when the clock is set to the correct time, the start gate voltage is removed, S1 closed and the clock can be started at the required moment with the start signal.

Fig. 1. 100 kHz separating amplifier

Fig. 2. Block diagramme of the solar clock

The 1 Hz solar second signal drives the :10 counter that drives the :6, 10 second counter which produces the 1 minute signal, which divided by 60 drives the hour counter dividing by 12, the output of which drives the divide by 2 p.m. (post meridiem) flip-flop. The 1, 2, 4, or 8 numbers shown on the right hand side of each s, 10s, m, 10m, h and p.m. divider show the weight of the incandescent lamp indicators on the time display. The incandescent lamp indicators are driven from separation amplifiers. One example of the total 38 such amplifiers, 19 lamps for each time solar and sidereal, is shown in fig. 3. The amplifier accepts the TTL logic signals and lights the lamp when the corresponding 1, 2, 4 or 8 output is 1, the lamp goes out when the signal is 0. The 1509 series resistor gives about 4 V voltage drop thus reducing the lamp voltage from 12 V to 8 V and the lamp current from 50 to 30 mA. The –4 V signals relative to ground are used as digital voltage indication of the actual time reading.

Fig. 3. Time indicator amplifier

Remote time indication by means of “normal” dial-clocks is accomplished with 1 s pulses driving a flip-flop. This flip-flop drives from its Q and Q outputs through a couple of gates a bridge power amplifier that produces voltage reversed pulse train for the dial-clock for remote time indication with 1 second resolution. The circuit diagramme of the dial-clock driving electronics is shown in fig. 4. The 1 Hz signals of 0.1 s duration appear at the output of the power amplifier, they have about 12 V amplitude and reverse their polarity each second. The dial clock drive voltage is fed to the clocks via the 1009 current limiting resistors which in case of a short circuit appearing on any remote clock line avoid wrong time indication on all remaining clocks. Two such circuits are used in this system one for the solar and another for the time. The circuit shown in fig. 4 can drive at least 10 dial-clocks of 4009 resistance each.

The generation of the sidereal second can be accomplished in numerous ways. The simplest, but least accurate digital divider, supplied with 100 kHz input frequency, has an error of about 4.35·10–7 i.e. 1 second in 26.62 days for a division ratio of 99727. Much higher accuracy can in principle be achieved by the use of much higher input frequency, because a better approximation of the sidereal to the solar time ratio-equal to 0.9972695664 is then possible. However the generation of the sidereal second with 10 decimal accuracy, quoted above, requires a 10 GHz input frequency! By using a 30 MHz input frequency and division by 29918087 one can obtain the sidereal second with 2,5·10–10 accuracy. Still another approach was used in Australia by Co1e et a1. (1971) who derive from a 99727 divider a long term accuracy of 10–9 for 100 ms intervals from 1 MHz input frequency. They add 100 ms every 64 hours by inclusion of a 64 h counter in the sidereal clock. This successful approach cannot be used with 100 kHz input frequency because then the required 640 hour counter would accumulate an error of 1 second before correction.

Fig. 4. Dial-clock driving electronics

Fig. 5. Sidereal clock with variable division ratio

The sidereal clock to be described is based on alternate division by 99727 and 99726. The division by 99727 regards the clock slowly and the division by 99726 accelerates it by a factor 22.06273 times greater than the retardation. But if one uses only the factor 22 the error is 2.73×10–8 which is less than one second in 424 days. The implementation of this idea requires the use of the divide by 23 counter which generates two time intervals, one of 22 and another of 1 time units. The simplified circuit diagramme of the sidereal clock with variable division ratio is shown in fig. 5. The 100 kHz signal is shaped and gated by the SN7400N integrated circuit before it enters the SN7490N decade frequency dividers. The appropriate 1, 2, 4 and 8 outputs of the five decades are applied to three 4 input NAND gates of the SN7420N type, that through 3 inverters and another 4 input gate followed by an inverter reset the counter on the 99727 count. The sidereal second pulses drive the divide by 23 counter which consists of one half of the SN7473 dual JK flip-flop the F.F.2 and the :16 binary counter of the SN7493N type. The 1 output of F.F.2 and the 2, 4 and 16 outputs of the SN7493N reset through proper gates the counter on the 23 count as well as the F.F.1. After one second the F.F.l toggles again and remains in this state for another 22 seconds. Thus one obtains the two intervals of 1 and 22 seconds duration that switch through a couple of 2 input gates the division ratio of 99727 for 22 seconds and that of 99726 for 1 second.

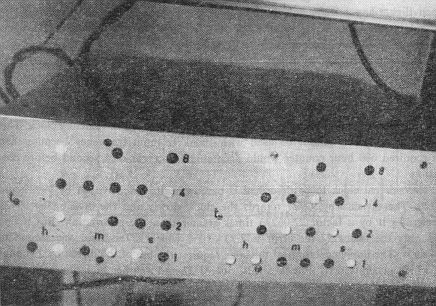

The sidereal second drives also another counter chain not shown in fig. 5, but identical to the one shown in fig. 2 which generates the seconds, minutes and hour time intervals. The sidereal clock employs the same 19 bit digital time indication as used in the solar clock. An overall view of the two 19 bit incandescent lamp time displays is shown in fig. 6. The solar time t⊙ indicated by the burning lamps is seen to be 11h 21m 14s a.m. while the sidereal clock shows t* 21h 24m25s or 9h 24m 25s p.m. For reasons of simplicity fig. 5 does not show the switches, similar to those used in the solar clock, that are used for setting the sidereal clock to the required time and starting it at the appropriate moment.

Fig.6. General view of the solar and sidereal time display

For calibration of automatic analogue paper chart recordings of radio astronomical observations both clocks produce two optional time marks. These marks are generated by proper bits from the 19 bit digital time indicating voltages. The circuit diagramme of one of the five time marker generators is shown in fig. 7. The required time indicating voltage step opens the transistor and discharges through the relay coil the 100 μF capacitor that shorts for a small fraction of a second the relay contacts that interrupt the signal flow to the recorder. This capacitor is recharged slowly via the 10 kΩ load resistor in about 1 second after the time indicating voltage disappears. Due to the 10 kΩ resistor this circuit cannot draw more than 1.2 mA from the supply in spite of the fact that the relay draws 120 mA when activated directly from a 12 V supply.

Fig. 7. Time marker generator

After more than two months of operation both clocks have given reliable service in spite of several mains failures.

The system described above has some noteworthy features such as:

— contact bounce is simply eliminated (in both clocks) by means of time setting at the 100 Hz level, thus nearly 100 contact bounce pulses are required to alter the time indication by 1 bit,

— the sidereal clock uses a new approach to increased accuracy of sidereal second generation by means of variable division ratio,

— time marks are insulated from the clock by means of a relay which does not draw appreciable current from the battery,

— no triggers are used in any circuit which results in reliable time indication due to the elimination of false triggering by noise,

— simple computer compatible time indication is used in both clocks by mean of 19 bit binary voltage levels.

Astronomical Institute

N. Copernicus University

Section of Radio Astronomy

Torun-Piwnice, Poland

REFERENCES

Cole D. J., Shimmins A. J. (1971), Proc. The Inst. of Radio and Electronics Engineers Australia 32, 12.

STRESZCZENIE

Zbudowano cyfrowy zegar na obwodach scalonych, generujący z 100 kHz termostatowanego kwarcowego oscylatora skalę czasową w czasie słonecznym i gwiazdowym z indykacją sekund, minut i godzin w okresie 1 doby. Indykacja każdego z czasów odbywa się w dwójkowym kodzie 19-bitowym W układzie 1, 2, 4, 8, w postaci wizualnej i napięciowej oraz przy pomocy mechanicznych zegarów wtórnych.

W generacji sekundy gwiazdowej zastosowano zmienny w czasie dzielnik częstości, dzielący 100 kHz na przemian przez 99727 i 99726, dający dokładność czasu gwiazdowego lepszą niż 1 sek. na rok.

Układ zasilany jest z akumulatora CdNi o pojemności 100 Ah, ładowanego buforowo z sieci prądu zmiennego 220V.

Instytut Astronomii

Uniwersytetu M. Kopernika

Zakład Radioastronomii

Toruń—Piwnice

[Posted by KMB on Feb 7, 2012]